西门子模块6ES322-5FF00-0AB0

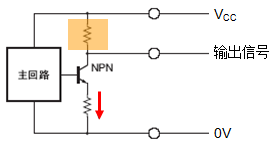

电压输出型

电压输出是在集电极开路输出电路的基础上,在电源和集电极之间接了一个上拉电阻,这样就使得集电极和电源之间能有了一个稳定的电压状态,如图2-5。一般在编码器供电电压和信号接受装置的电压一致的情况下使用这种类型的输出电路。

图2-5 电压输出型

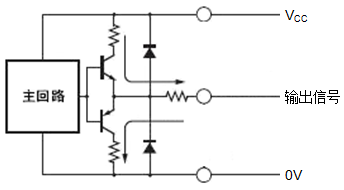

2.3 推挽式输出

推挽式输出方式由两个分别为 PNP 型和 NPN 型的三极管组成,如图2-6所示。当其中一个三极管导通时,另外一个三极管则关断,两个输出晶体管交互进行动作。

这种输出形式具有高输入阻抗和低输出阻抗,因此在低阻抗情况下它也可以提供大范围的电源。由于输入、输出信号相位相同且频率范围宽,因此它还适用于长距离传输。

推挽式输出电路可以直接与 NPN 和 PNP 集电极开路输入的电路连接,即可以接入源型或漏型输入的模块中。

图2-6 推挽式输出

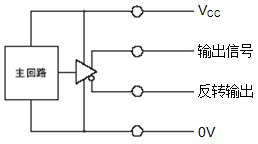

2.4 线驱动输出

如图 2-7所示,线驱动输出接口采用了专用的 IC 芯片,输出信号符合RS-422 标准,以差分的形式输出,因此线驱动输出信号抗干扰能力更强,可以应用于高速、长距离数据传输的场合,同时还具有响应速度快和抗噪声性能强的特点。

图2-7 线驱动输出

说明:除了上面所列的几种编码器输出的接口类型外,现在好多厂家生产的编码器还具有智能通信接口,比如PROFIBUS总线接口。这种类型的编码器可以直接接入相应的总线网络,通过通信的方式读出实际的计数值或测量值,这里不做说明。

3 高速计数模块与编码器的兼容性

高速计数模块主要用于评估接入模块的各种脉冲信号,用于对编码器输出的脉冲信号进行计数和测量等。西门子SIMATIC S7的全系列产品都有支持高速计数功能的模块,可以适应于各种不同场合的应用。

根据产品功能的不同,每种产品高速计数功能所支持的输入信号类型也各不相同,在系统设计或产品选型时要特别注意。下表3-1给出了西门子高速计数产品与编码器的兼容性信息,

√兼容; - 不兼容

4 编码器使用的常见问题 4.1 编码器选型时要考虑哪些参数

在编码器选型时,可以综合考虑以下几个参数:

? 编码器类型:根据应用场合和控制要求确定选用增量型编码器还是性编码器。

? 输出信号类型:对于增量型编码根据需要确定输出接口类型(源型、漏型)。

? 信号电压等级:确认信号的电压等级(DC24V、DC5V等)。

? 输出频率:根据应用场合和需求确认输出频率及分辨率、位数等参数。

? 安装方式、外形尺寸:综合考虑安装空间、机械强度、轴的状态、外观规格、机械寿命等要求。

4.2 如何判断编码器的好坏

可以通过以下几种方法判断编码器的好坏:

? 将编码器接入 PLC的高速计数模块,通过读取实际脉冲个数或码值来判断编码器输出是否正确。

? 通过示波器查看编码器输出波形,根据实际的输出波形来判断编码器是否正常。

? 通过万用表的电压档来测量编码器输出信号电压来判断编码器是否正常,具体操作方法如下:

1)编码器为NPN晶体管输出时,用万用表测量电源正极和信号输出线之间的电压

· 导通时输出电压接近供电电压

· 关断时输出电压接近 0V

2)编码器为PNP晶体管输出时,用万用表测量测量电源负极和信号输出线之间的电压

· 导通时输出电压接近供电电压

· 关断时输出电压接近 0V

西门子PLC卡件6ES7317-6TK13-0AB0

4.3 计数不准确的原因及相应的避免措施

在实际应用中,导致计数或测量不准确的原因很多,其中主要应注意以下几点:

? 编码器安装的现场环境有抖动,编码器和电机轴之间有松动,没有固定紧。

? 旋转速度过快,超出编码器的响应频率。

? 编码器的脉冲输出频率大于计数器输入脉冲频率。

? 信号传输过程中受到干扰。

针对以上问题的避免措施:

? 检查编码器的机械安装,是否打滑、跳齿、齿轮齿隙是否过大等。

? 计算一下脉冲频率,是否接近或超过了极限值。

? 确保高速计数模块能够接收的脉冲频率大于编码器的脉冲输出频率。

? 检查信号线是否过长,是否使用屏蔽双绞线,按要求做好接地,并采取必要抗干扰措施。

4.4空闲的编码器信号线该如何处理

在实际的应用中,可能会遇到不需要或者模块不支持的信号线,例如:

? 对于带零位信号的AB正交编码器(A、B、N),模块不支持N相输入或者不需要Z信号。

? 对于差分输出信号(A、/A,B、/B,N、/N),模块不支持反向信号(/A,/B,/N)的输入。

对于这些信号线,不需要特殊的处理,可以直接放弃不用!

4.5增量信号多重评估能否提高计数频率

对于增量信号,可以组态多重评估模式,包括双重评估和四重评估。四重评估是指同时对信号 A 和B 的正跳沿和负跳沿进行判断,进而得到计数值,如图4-1所示。对于四重评估的模式,因为对一个脉冲进行了四倍的处理(四次评估),所以读到的计数值是实际输入脉冲数的四倍,通过对信号的多重评估可以提高测量的分辨率。

图4-1 四重评估原理图

通过以上对增量信号多重评估原理的分析可以看出,多重评估只是在原计数脉冲的基础上对计数值作了倍频处理,而实际上对实际输入脉冲频率没有影响,所以也不会提高模块的计数频率。例如,FM350-2的计数频率为10kHz,那么即使配置为四重评估的模式,其的计数频率还是10kHz。

所有输入元件(输入继电器)及内部辅助继电器、输出继电器所处的某种工作状态,简称逻辑条件。它所对应的接点电路输出应该是唯一的。要想用相同的逻辑条件产生不同的输出,是不可能的,称接点电路正常工作的唯一性原则,是电路正常工作必须遵守的条件。从本质上讲,这是因为逻辑与接点输出之间的关系为组合逻辑函数关系,而组合逻辑函数是单值函数,一种输入只对应一种输出。违背这个原则设计的接点电路,逻辑上是混乱的,称为逻辑条件相混,其设计意图也是不可能实现的。

梯形图电路多为时序电路,仅输出继电器与输入继电器之间的关系而言,不是唯一对应的,这里主要的输出继电器、内部辅助继电器都有“记忆”的作用,可用本身接点反馈,也可用置位指令,实现这个“记忆”。前面提到,时序电路的工作是按节拍展开的。内部辅助及输出继电器若有多个连续的ON的节拍,把个节拍定义为起动节拍,其相应的动作称起动;连续ON后的个OFF节拍定义为结束节拍,其相应的动作称结束。有了这个定义,梯形图电路的唯一性原则可表述为:在某种逻辑条件下,所对应的内部辅助及输出继电器的起动、结束应是唯一的。要想在相同的逻辑条件下,使辅助及输出继电器在某个节拍起动(或结束)是不可能的。这是因为,时序电路“分解”之后,起动与结束分别也都是组合逻辑函数,也是单值的,因而也应遵循这个原则。

梯形图出现相混时,可适当增加内部辅助继电器,以增加反映逻辑条件的变量,并因此把相混分开。从理论上讲,每增加一个内部辅助继电器,即可使可区分的状态增加一倍。

唯一性原则给梯形图设计,或plc编程增加了约束,但也给进行设计和编程带来了入手思路。

这里介绍的解析编程就是从分析唯一性原则入手的,具体步骤是:

1)列原始通电表:根据PLC工作对象的情况,划分工作节拍,并确定各个节拍的输入与输出的对应关系,列初始通电表,这个表也称原始通电表。它仅是设计要求的“表格化”而已,用它可反映输出与输入在各个节拍的对应关系。

2)唯一性设计:对原始通电表进行唯一性检查,若有相混的节拍时,用增加内部辅助电器的方法加以区分。然后,再查所加的辅助继电器工作是否符合唯一性原则。若也有相混的,再加、再查,直至全部满足唯一性原则为止。

3)列逻辑表达式:根据通电表列出各输出继电器及内部辅助继电器的逻辑表达式。

4)化简逻辑式:对逻辑表达式进行化简,以得到简式。

5)画梯形图:依简式画梯形图。

| 如果把plc的梯形图理解为电路,若按输入与输出的关系分,则有组合电路与时序电路两种,若按输入的确定性情况分,有确定电路与随机电路两种。 1、组合电路 凡是输出仅与输入的当前情况有关,而与输入的历史情况无关的梯形图,称为组合电路。其特点是: 1)无反馈,或不用锁存(或置位)及计数指令。 2)输出的状态仅由输入元件状态的组合直接反映,其结果是唯一的。 3)电路状态转换,可以一次实现,没有中间状态的过渡。 4)所需输入元件多,但电路简单可靠。 2、时序电路 凡是输出不仅与输入的当前情况有关,而且还与输入的历史状况有关的梯形图,称为时序电路。简单的时序电路,就是带有自锁环节的起停电路。时序电路的特点是: 1)反馈:其输出线圈不仅受输入信号控制,还直接或间接受自身接点的控制,或是用了计数或锁存(或置位)指令,能记住输入信号已经作用过的状况。 2)多解:同样的输入现况,可以有多种输出。其间的不同,是由输入的历史状况区分的。电路的历史状况可用计数器、锁存器(或置位)记录,也可用通过自身接点的反馈去做相应的记录。 3)顺序:时序电路的多解的实际取值是由其工作顺序确定的。而工作顺序又是一个节拍、一个节拍展开的。所谓节拍是指两次输入的时间间隔。对PLC而言,输入仅看成是外端的,内部器件间的互相作用或自作用(反馈),可不必与继电器电路一样,也看成输入。它是顺序执行指令实现控制的,不存在继电器电路那样的竞争问题,故不必把节拍分得很细。 节拍也可用输出变化划分,即把它定义为两次输出变化间的时间间隔。分析时序电路一般要一个节拍、一个节拍地分析,设计时序电路,也要一个节拍、一个节拍地考虑。 时序电路由于记忆的缘故,所需的输入元件少些。这对于一些难以使用较多的输入信号的场合,是一个很大的方便。但时序电路相对也比组合电路复杂些。研究时序,总是假设: ①同一时间仅存在一个输入。 ②两次输入的间隔足以使PLC执行完所有指令。 多数的PLC梯形图是时序电路,而且这两条假设,也总是能被满足的。 应该指出,这里讲的时序电路都是异步时序电路,节拍转换没有统一的同步脉冲信号进行控制。 3、确定电路 如果控制对象工作过程或顺序是确定的,与其对应的控制电路即为确定电路。多数PLC梯形图为确定电路。 确定电路的设计首先要弄清这个确定的过程或顺序,然后再依过程的展开或顺序的推进情况逐步地设计。 确定电路有组合的,也有时序的。不过,时序的更多些,因为既是确定的,把它设汁成时序的,输入信号可以减少。 确定电路可用通电表反映它的工作情况。 4、随机电路 如果对象的工作过程或顺序不是确定的,或是不固定不变的,其对应的控制电路即为随机电路。 随机电路也可列通电表,那就要把它所有的可能情况都列出(如能看得清楚,“对称”的情况也可不列)。随机电路的设计过程是分别可能的情况,逐一分析它的工作过程,然后分别作设计,后在综合在一起,即为所设计的电路。 |